Tim Edwards

VP Analog and Platform

efabless

efabless.com

Open Circuit Design opencircuitdesign.com

- A brief history of SCMOS

- A proposal for an open PDK Framework

- The New Golden Age of Open Silicon

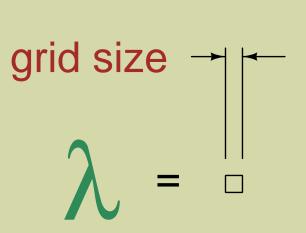

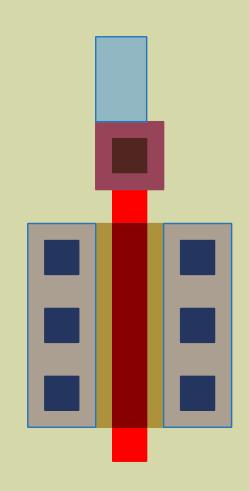

SCMOS = Scalable CMOS

Once upon a time in the 1980s. . .

SCMOS = Scalable CMOS

lambda (unitless)

SCMOS = Scalable CMOS

lambda (unitless)

minimum gate length =  $2\lambda$

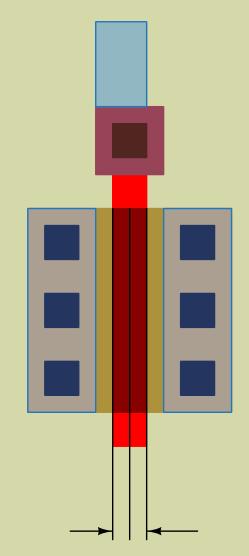

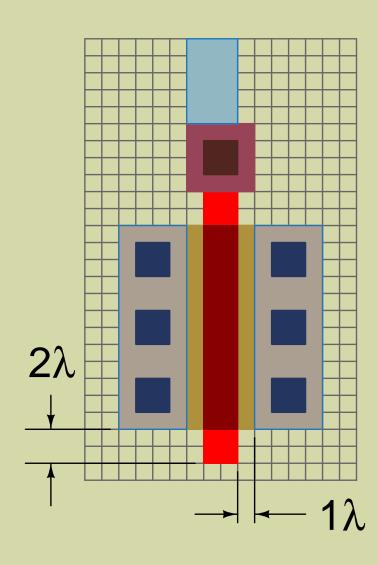

## SCMOS = Scalable CMOS

- minimum gate length =  $2\lambda$

- minimum metal width =  $3\lambda$

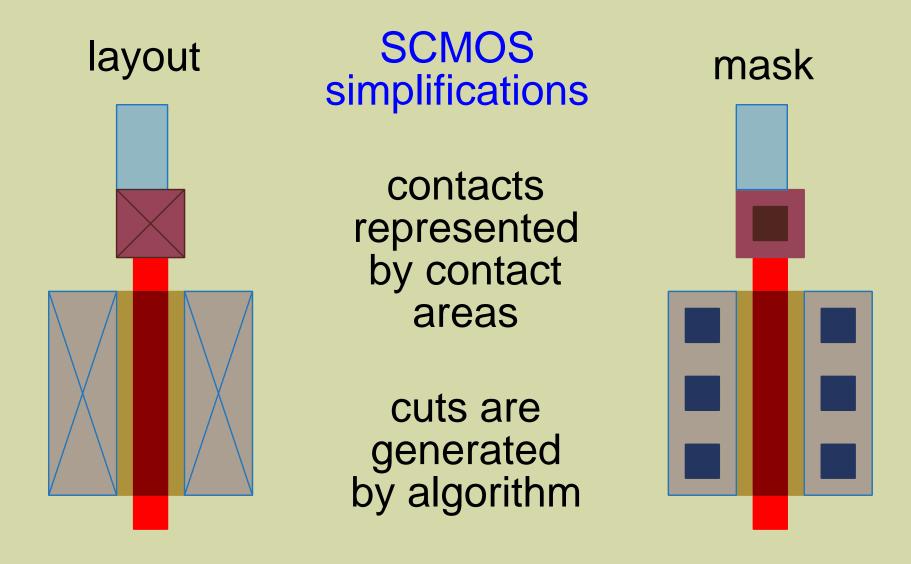

- contact (cut + surround) width =  $4\lambda$

- poly extension of gate =  $2\lambda$

- poly to diffusion contact spacing =  $1\lambda$

"reinvented" as LEF

"VIARULE GENERATE"

One benefit of SCMOS: Long-term viability

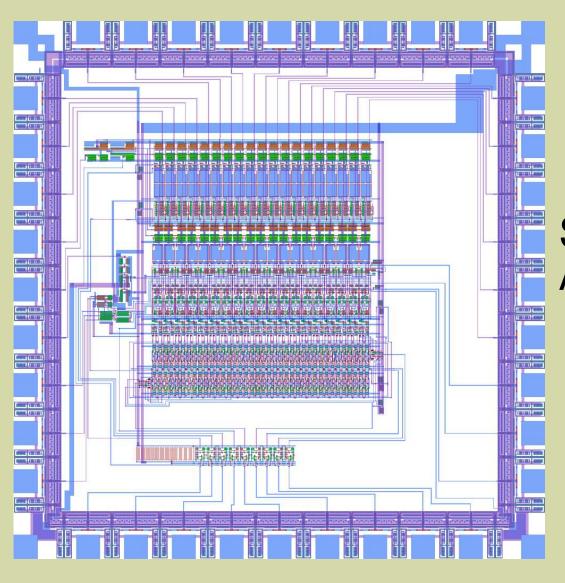

SCMOS is forever: A layout I did in 1997

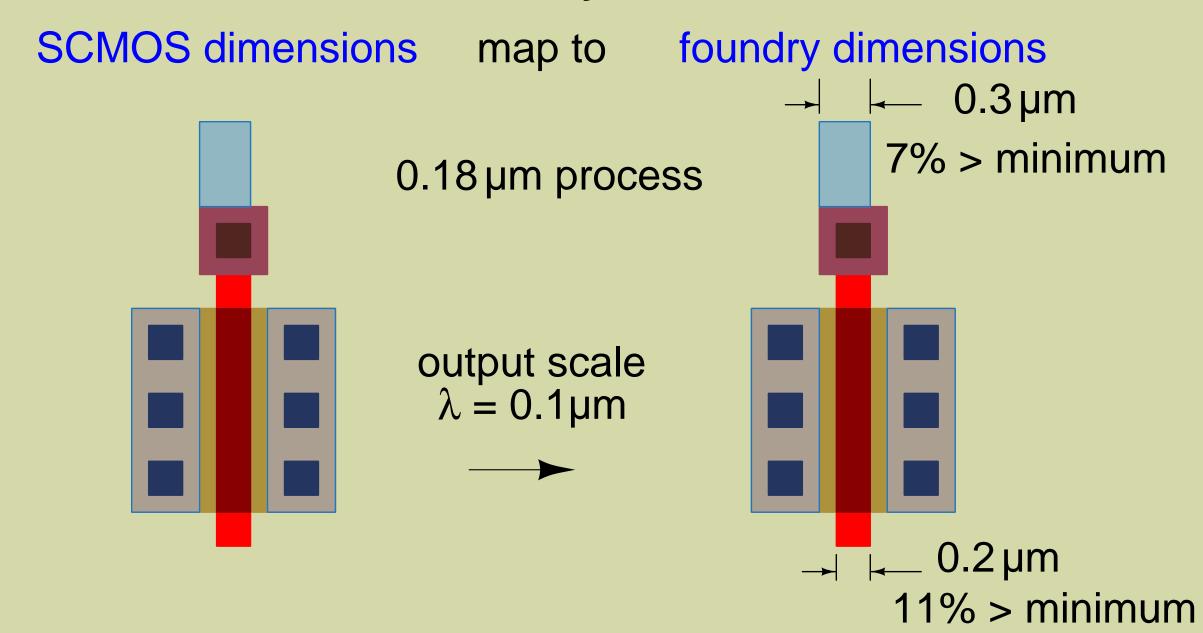

Prime benefit of SCMOS: Natural obfuscation

Foundry rules cannot be reverse-engineered from SCMOS rules.

Layouts can be published and shared.

However. . .

Foundry rules *can* be reverse-engineered from the output generation mapping rules.

Solution: Services like MOSIS map SCMOS layout to foundry mask layout

Prime benefit of SCMOS: Natural obfuscation

Foundry rules cannot be reverse-engineered from SCMOS rules.

Layouts can be published and shared.

Also...

Cannot simulate without models, which are foundry-proprietary

Solution: Cloud-based simulation?

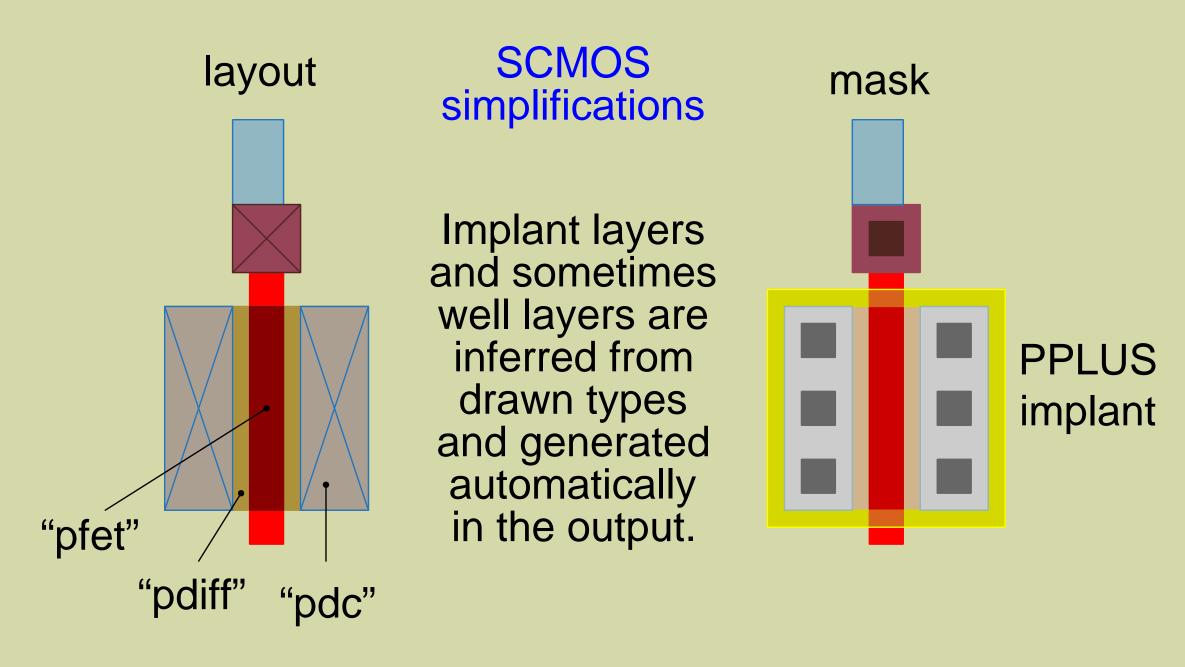

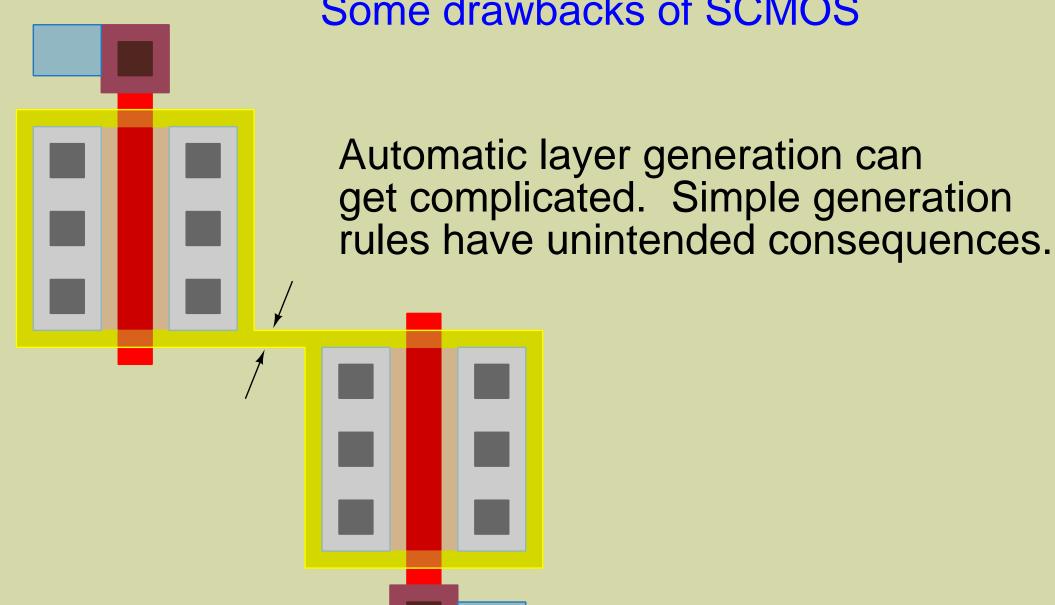

Some drawbacks of SCMOS

Some drawbacks of SCMOS

Scalable CMOS is not really scalable below about 0.25 µm processes

Too many one-off DRC rules

Rules that don't map well to multiples of  $\lambda$

But...

SCMOS rules work and simplify design even if they cannot scale between processes.

- A brief history of SCMOS

- A proposal for an open PDK Framework

- The New Golden Age of Open Silicon

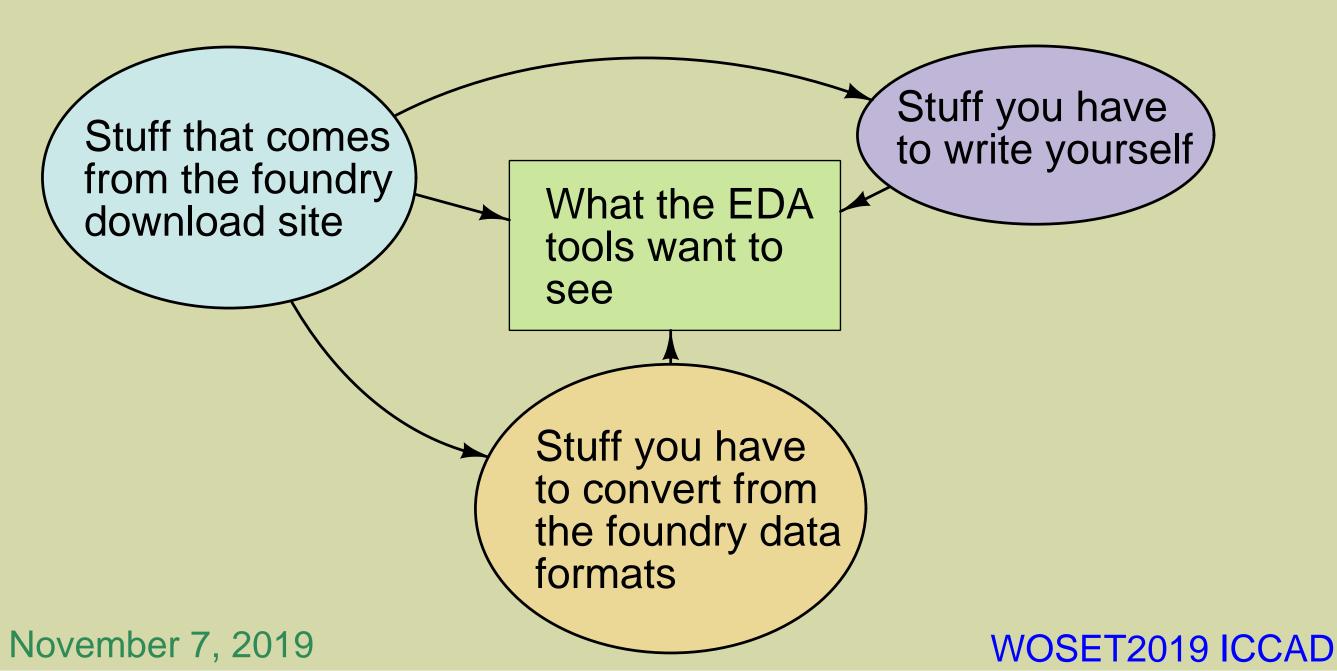

The Vicious Cycle

No direct foundry support for SCMOS

No Open Source EDA tool adoption

No commercial tool support for SCMOS

No foundry support for Open Source EDA tools using SCMOS

The Vicious Cycle

No direct foundry support for \_\_\_\_\_

Insert any community- proposed method here

No Open Source EDA tool adoption

No commercial tool support for

No foundry support for Open Source EDA tools using

**7**

### Solutions?

- Open source EDA tools with correct-by-design layout output (OpenROAD, OpenRAM)

- Translation services between obfuscated and foundry rules (efabless)

- Foundries with open processes (stay tuned. . .)

- A common framework for community-inspired tools (the rest of this talk)

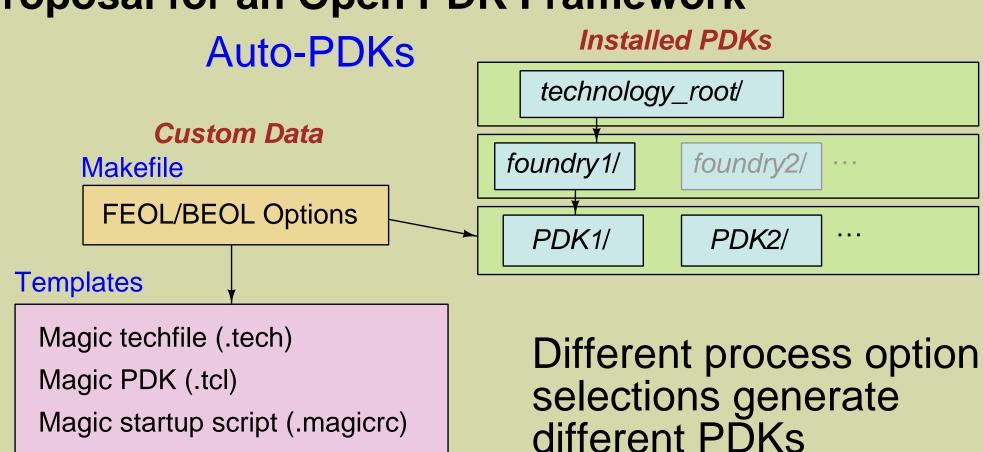

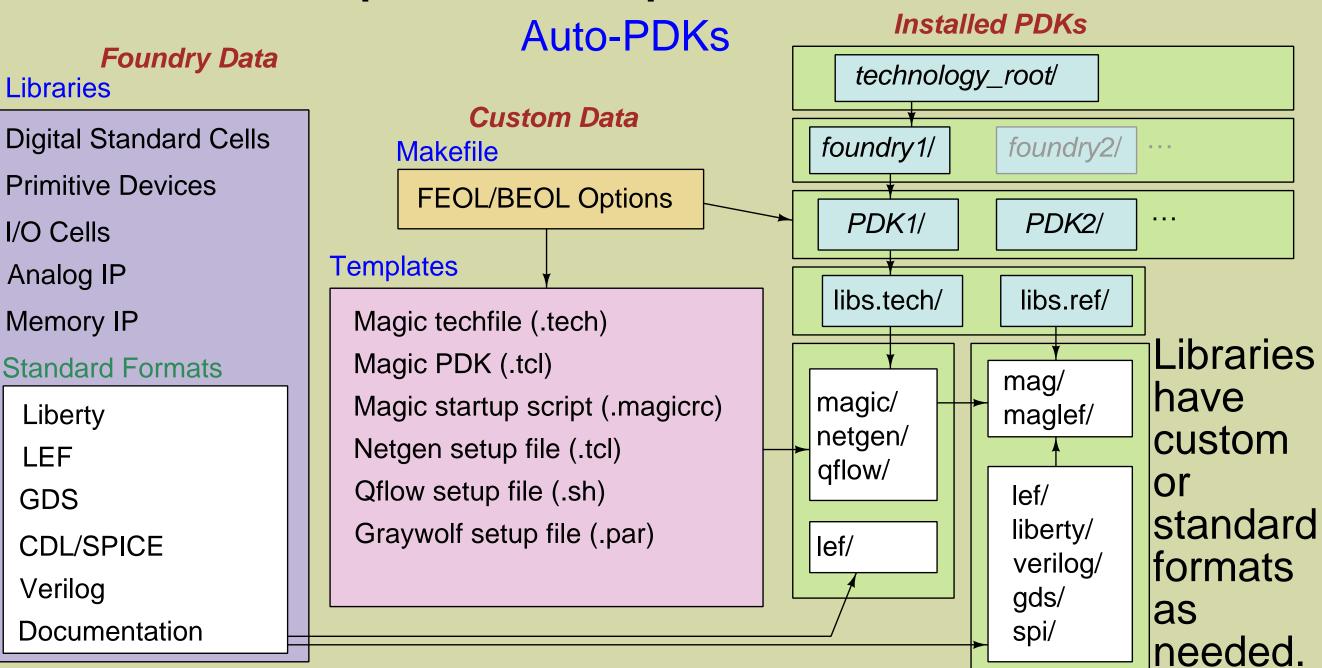

Auto-PDKs (provisional name)

**Auto-PDKs**

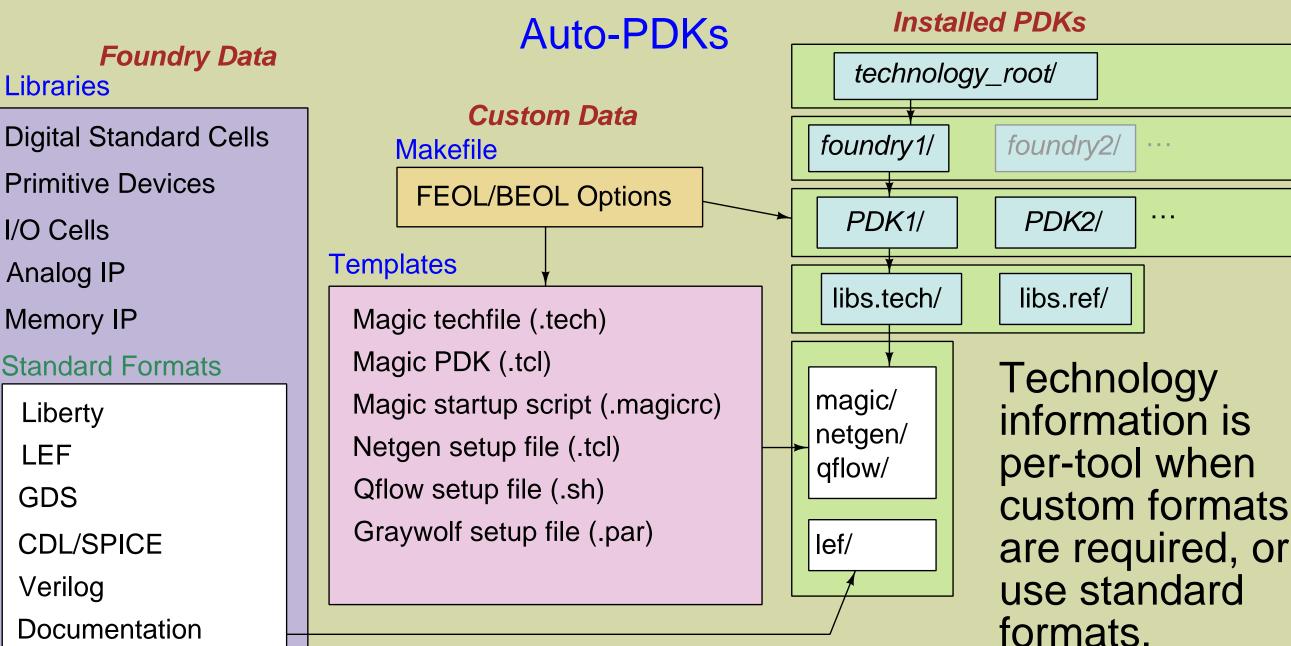

### Foundry Data

Libraries

Digital Standard Cells

**Primitive Devices**

I/O Cells

Analog IP

Memory IP

**Standard Formats**

Liberty

LEF

**GDS**

CDL/SPICE

Verilog

Documentation

Start with foundry download data.

Hopefully this comes in standard formats.

Foundry Data

Libraries

**Digital Standard Cells**

**Primitive Devices**

I/O Cells

Analog IP

Memory IP

**Standard Formats**

Liberty

LEF

**GDS**

CDL/SPICE

Verilog

Documentation

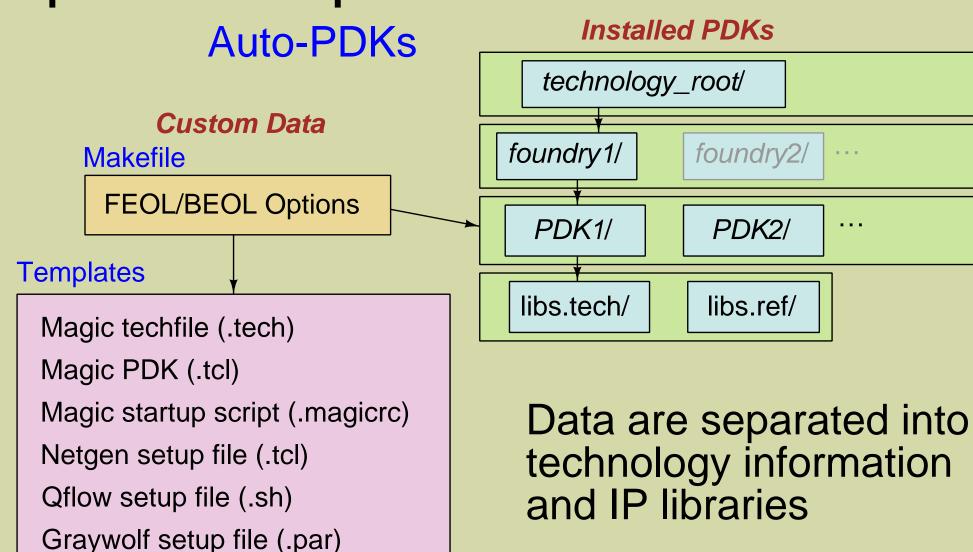

**Auto-PDKs**

**Custom Data**

Makefile

FEOL/BEOL Options

**Templates**

Magic techfile (.tech)

Magic PDK (.tcl)

Magic startup script (.magicrc)

Netgen setup file (.tcl)

Qflow setup file (.sh)

Graywolf setup file (.par)

Makefile-driven system

Each open-source EDA tool will need to contribute template files for the process.

Netgen setup file (.tcl)

Qflow setup file (.sh)

Graywolf setup file (.par)

**Foundry Data**

Libraries

**Digital Standard Cells**

**Primitive Devices**

I/O Cells

Analog IP

Memory IP

**Standard Formats**

Liberty

LEF

**GDS**

CDL/SPICE

Verilog

Documentation

November 7, 2019

# Foundry Data

Libraries

**Digital Standard Cells**

**Primitive Devices**

I/O Cells

Analog IP

Memory IP

### **Standard Formats**

Liberty

LEF

**GDS**

CDL/SPICE

Verilog

Documentation

November 7, 2019

**WOSET2019 ICCAD**

# Benefits of an open framework

- Easier development of open source EDA tools

- Set of example (real) processes always available

- For open PDKs, direct download from repo like github

- More community development of tools and PDKs

- More community use of open source EDA tools

- More community design, more creativity

- A brief history of SCMOS

- A proposal for an open PDK Framework

- The New Golden Age of Open Silicon

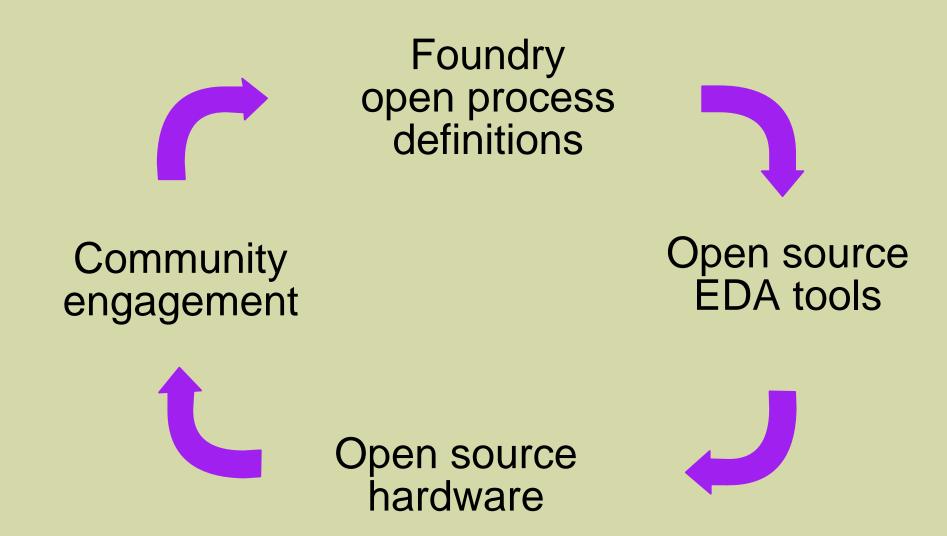

The Virtuous Cycle

Clever design can beat raw performance.

Open community design = massively distributed design

Massively distributed design is more valuable than any proprietary algorithm in a CAD tool.

Open source EDA tools, open process PDKs, and open hardware will create the New Golden Age of Open Silicon.

# The New Golden Age of Open Silicon The beginning of the new Golden Age of Open Silicon is now. November 7, 2019