# SystemVerilog IDE integration with Verible Language Server Support

Henner Zeller | WOSET 2021

# Verible is a suite of SystemVerilog tools

- Verible is a suite of SystemVerilog code quality and introspection tools.

- Started by David Fang, shown on WOSET 2018, published by Google in 2019 under Apache license and now under Chips Alliance roof.

#### **Tools**

- Command line

- direct project use

- Github integration

- automatic review

- Language server

- features available directly in editor/IDE

# Command Line Utility: Linting with

verible-verilog-lint

# Avoid potential bugs with linter

```

verible@WOSET-2021$ cat truncated_numeric_literal.sv

module truncated_numeric_literal;

assign a = 4'h1F;

endmodule

verible@WOSET-2021$ verible-verilog-lint truncated_numeric_literal.sv

truncated_numeric_literal.sv:2:17: Number 4'h1F occupies 5 bits, truncated to 4 bits. [Style: number-literals] [truncated-numeric-literal]

verible@WOSET-2021$

```

# Highlight readability issues

For example if you always want to have bit-patterns written with all digits, e.g. 4'b0001 ... there is a rule for that.

```

verible@WOSET-2021$ cat undersized_binary_literal.sv

module undersized_binary_literal;

localparam logic [3:0] Foo = 4'b1;

endmodule

verible@WOSET-2021$ verible-verilog-lint undersized_binary_literal.sv

undersized_binary_literal.sv:2:35: Binary literal 4'b1 has less digits than expected for 4 bits. [Style: number-literals] [undersized-binary-literal]

verible@WOSET-2021$ ■

```

# ... and apply available autofix

```

verible@WOSET-2021$ verible-verilog-lint --autofix=inplace-interactive undersized_binary_literal.sv

undersized binary literal.sv:2:35: Binary literal 4'b1 has less digits than expected for 4 bits. [Style:

number-literals] [undersized-binary-literal]

[ 1. Alternative Left-expand leading zeroes ]

@@ -1.3 +1.3 @@

module undersized binary literal;

localparam logic [3:0] Foo = 4'b1;

+ localparam logic [3:0] Foo = 4'b0001;

endmodule

[ 2. Alternative Replace with decimal ]

@@ -1,3 +1,3 @@

module undersized binary literal;

localparam logic [3:0] Foo = 4'b1;

+ localparam logic [3:0] Foo = 4'd1;

endmodule.

Autofix is available. Apply? [1,2,y,n,a,d,A,D,p,P,?] 1

verible@WOSET-2021$ cat undersized_binary_literal.sv

module undersized_binary_literal;

localparam logic [3:0] Foo = 4'b0001;

```

endmodule

verible@WOSET-2021\$

# There are many rules available

- There are close to 60 rules available now, and it relatively easy to add more

- Each rule can be enabled or disabled in your project either with a command line or a configuration file.

- Waiver files allow for fine-grained control per file and line

Lint rules are auto-documented on this page https://chipsalliance.github.io/verible/lint.html

#### Or on the command line

verible-verilog-lint --help\_rules=all

#### nacro-string-concatenation

Concatenation will not be evaluated here. Use "..." instead. See [Style: defines].

Enabled by default: false

#### mismatched-labels

Check for matching begin/end labels. See [Style: mismatched-labels]

Enabled by default: false

#### module-begin-block

Checks that there are no begin-end blocks declared at the module level. See [Style: floating-begin-end-blocks].

Enabled by default: true

#### module-filename

If a module is declared, checks that at least one module matches the first dot-delimited component of the file name. Depending on configuration, it is also allowed to replace underscore with dashes in filenames. See [Style: file-names].

Parameter

# Command Line Utility: Formatting with

verible-verilog-format

# The formatter prettifies

#### In-place formatting

```

module my module #(

width = 2,

my pkg::length t length = 4

input logic clk,

input wire [7:0] data,

output reg

initial begin

foo[0] <= 1'b1;

bar <= 1'b0;

next <= prev ^ xyz;</pre>

end

endmodule

```

#### Interactive session...

# Github integration

# A github action provides reviews

Use the provided github action to directly comment in your pull requests <a href="https://github.com/chipsalliance/verible-linter-action">https://github.com/chipsalliance/verible-linter-action</a>

```

rtl/ibex_multdiv_slow.sv

input logic

rst ni,

input logic

mult_en_i, // dynamic enable signal, for FSM control

input logic

div_en_i, // dynamic enable signal, for FSM control

input logic

mult_sel_i, // static decoder output, for data muxes

input logic

div_sel_i, // static decoder output, for data muxes

22

input ibex pkg::md op e operator i,

22

input ibex_pkg::md_op_e operator i,

github-actions (bot) 23 days ago

[verible-verilog-lint] reported by reviewdog ♥

Use spaces, not tabs. [Style tabs] [no-tabs]

```

### Verible: other tools

- verible-verilog-project -- extracting dependencies, creating file-lists etc.

- <u>verible-verilog-kyte-extractor</u> -- Generate a kythe index to cross-reference code

- verible-verilog-diff -- lexical comparison to verify contents

- verible-verilog-preprocess

- verible-verilog-obfuscate -- obfuscated test case preparation

- Preserves byte/line offsets within files, to retain diagnostic locations

- Supports multi-file operation, saving obfuscation maps, and decoding

# IDE integration with Language server

verible-verilog-ls

### A Language Server augments your IDE

- The Language Server Protocol (LSP) is a standard protocol that allows external tools provide useful features to editors and IDEs. These tools are called language servers.

- Features can show syntax and linting issues, formatting code, providing fixes or refactoring features.

- Implementing the protocol, Verible now can provide its features directly in your IDE

- Most editors used for programming provide some LSP integration;

verible-verilog-ls has been tested with emacs, vi, sublime, kate and vscode.

The Verible language server verible-verible-ls provides edit-enhancing features via the language server protocol.

# Find issues while typing...

```

// Assume that rst_ni is low for the first cycle and not true after that.

assume (~((f_startup_count == 2'd0) ^ ~rst_ni));

// There is a feed-through path from branch_i to req_o which isn't squashed when in reset. Assume

// that branch_i isn't asserted when in reset.

assume (`IMPLIES(!rst_ni, !branch_i));

end

// Several of the protocol checks are only valid when there is a valid address. This is false

// after reset. It becomes true after any branch after reset and then false again on any returned

// error (because the straight-line address depends on the presumably-bogus rdata).

logic f_addr_valid;

always_ff @(posedge clk_i or negedge rst_ni) begin

if (!rst ni) begin

f_{addr_valid} = 1'b0;

end else begin

if (branch_i) begin

f_addr_valid = 1'b1;

encrelse if (valid_o & readu_i & err_o) begin

f addr valid = 1'b0;

end

Use blocking assignments, at most, for locals inside 'always ff' sequential blocks, [Style: sequential-logic][always-ff-non-blocking]

end

// Reset assumptions

(Verilog Flymake[◊ ○ 35] WK EditorConfig LSP[verible-ls:22515])

-:**- formal_tb.sv

13% L116 Git-master

```

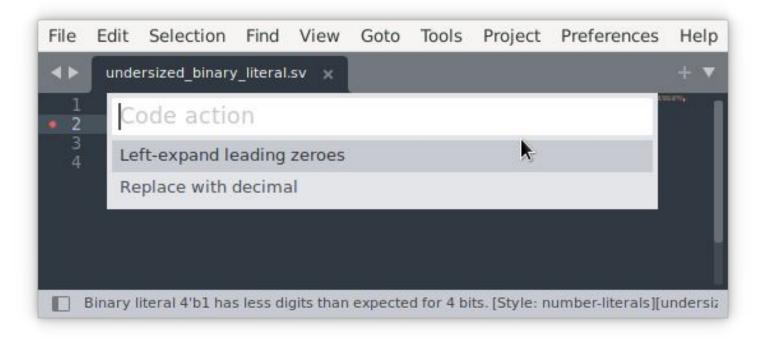

## Language Server: show lint violation

```

File

Edit

Selection Find View Goto

Tools

Project

Preferences

Help

undersized binary literal.sv x

module undersized binary literal; localparam logic [3:0] Foo = 4'b

Binary literal 4'b1 has less digits than expected for 4 bits.

[Style: number-literals][undersized-binary-literal] (fix

available) verible

[verible-verilog-ls] Code action: choose code action (2 available)

verible-verilog-Is, Line 1, Column 1; No definition found for b1

```

# Language Server: choose the fix

# Done. Fix applied.

```

Selection Find View Goto

Project

Preferences

File

Edit

Tools

Help

undersized binary literal.sv ...

module undersized binary literal; localparam logic [3:0] Foo = 4'b0001; T

endmodule

verible-verilog-ls, Line 2, Column 39

Spaces: 2

```

### Hierarchy view shows block labels

```

Edit View Projects LSP Client Bookmarks Sessions Tools Settings Help

Documents

Symbols

ibex id stage.sv

ПП

▼ ibex id stage

IMM B U,

Balu_operand_a_mux

Balu_muxes

Babt_immediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

IMM B J.

IMM B INCR PC.

IMM B INCR ADDR})

end

// ALU MUX for Operand B

386

assign alu operand b = (alu op b mux sel == OP B IMM) ? imm b : rf rdata b fwd;

Git 🛅

// Multicycle Operation Stage Register //

A intermediate val reg

A rf wdata id mux

392 ▼

for (genvar i = 0; i < 2; i++) begin : gen intermediate val reg

a csr pipeline flushes

393 🔻

always ff @(posedge clk i or negedge rst ni) begin : intermediate val reg

品 g branch set direct

394 ▼

if (!rst ni) begin

🔒 g branch set flop

imd val q[i] \ll 0;

Filesystem

end else if (imd val we ex i[i]) begin

396

R g sec branch taken

imd val q[i] <= imd val d ex i[i];</pre>

B g nosec branch taken

end

🔠 id pipeline reg

end

agen stall mem

end

401

A gen no stall mem

assign imd val q ex o = imd val q;

403

404

405

// Register File MUX //

406

407

Line 393, Column 50

Soft Tabs: 4 *

UTF-8 - SystemVerilog -

□ Output 🗟 Search and Replace 🗏 Current Project 🖸 Terminal Panel 🖽 LSP Client

Filter...

```

# Immediate update with your edits

```

Edit View Projects LSP Client Bookmarks Sessions Tools Settings Help

Documents

Symbols

ibex id stage.sv

▼ ibex id stage

IMM B U,

Balu_operand_a_mux

Balu_muxes

Babt_immediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

Balimmediate_b_mux

IMM B J.

IMM B INCR PC.

IMM B INCR ADDR})

end

// ALU MUX for Operand B

386

assign alu operand b = (alu op b mux sel == OP B IMM) ? imm b : rf rdata b fwd;

// Multicycle Operation Stage Register //

▼ ☐ intermediate val reg

390

₽ foo

392 ▼

for (genvar i = 0; i < 2; i++) begin : gen intermediate val reg

A rf wdata id mux

393 ▼

always ff @(posedge clk i or negedge rst ni) begin : intermediate val reg

R csr pipeline flushes

394

if (!rst ni) begin : foo

₽ g branch set direct

imd val q[i] \ll 0;

Filesystem

end else if (imd val we ex i[i]) begin

396

R g branch set flop

imd val q[i] <= imd val d ex i[i];</pre>

B g sec branch taken

end

🔓 g nosec branch taken

end

a id pipeline reg

end

401

🔒 gen stall mem

402

assign imd val q ex o = imd val q;

agen no stall mem

403

404

405

// Register File MUX //

406

407

Line 394, Column 31

Soft Tabs: 4 *

UTF-8 - SystemVerilog -

□ Output 🗟 Search and Replace 🗏 Current Project 🖸 Terminal Panel 🖽 LSP Client

Filter...

```

\$finish;

endtask

endmodule

https://github.com/chipsalliance/verible