# 8bitworkshop

An Interactive Verilog Learning Tool

# Introduction 8bitworkshop.com

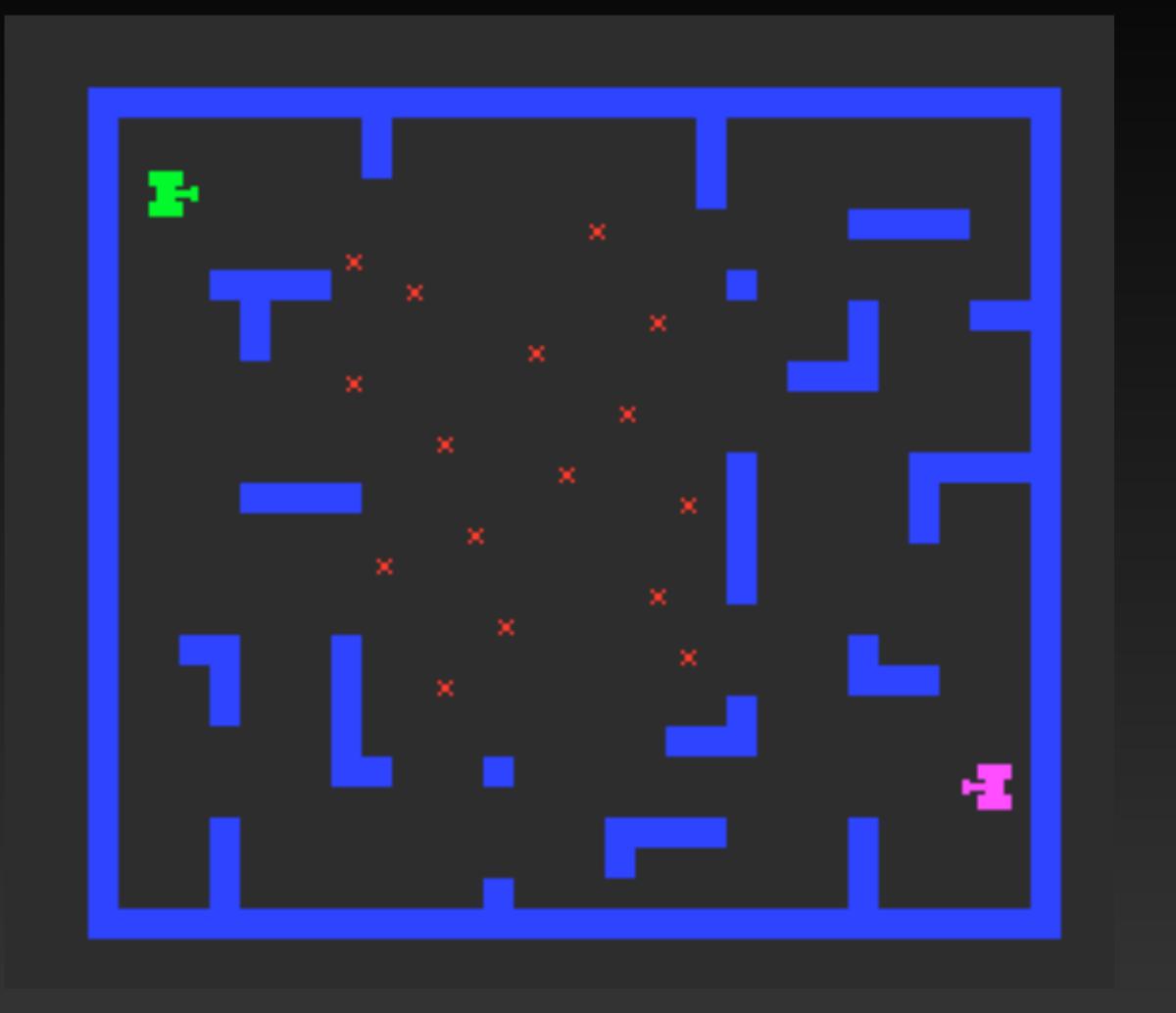

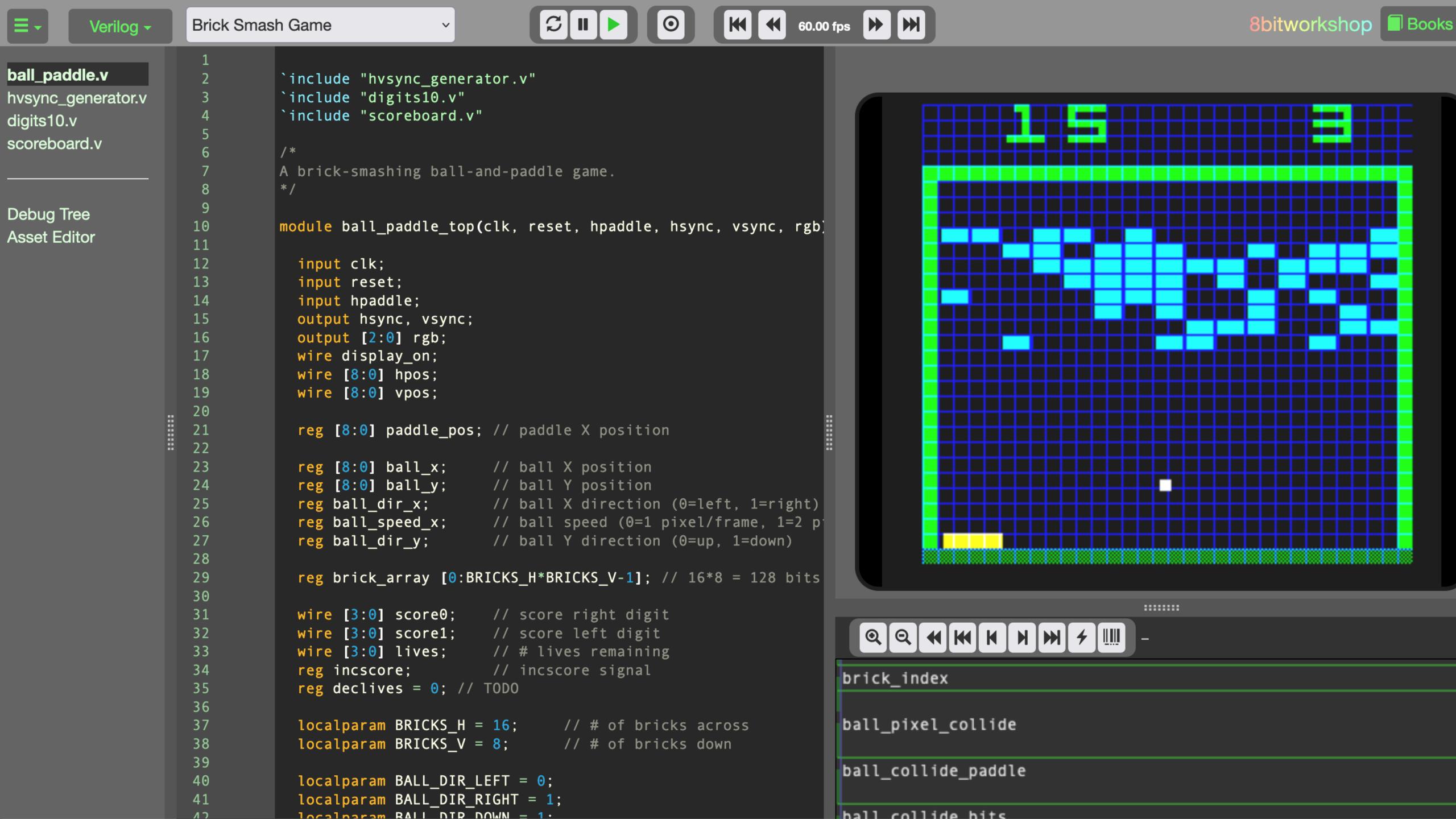

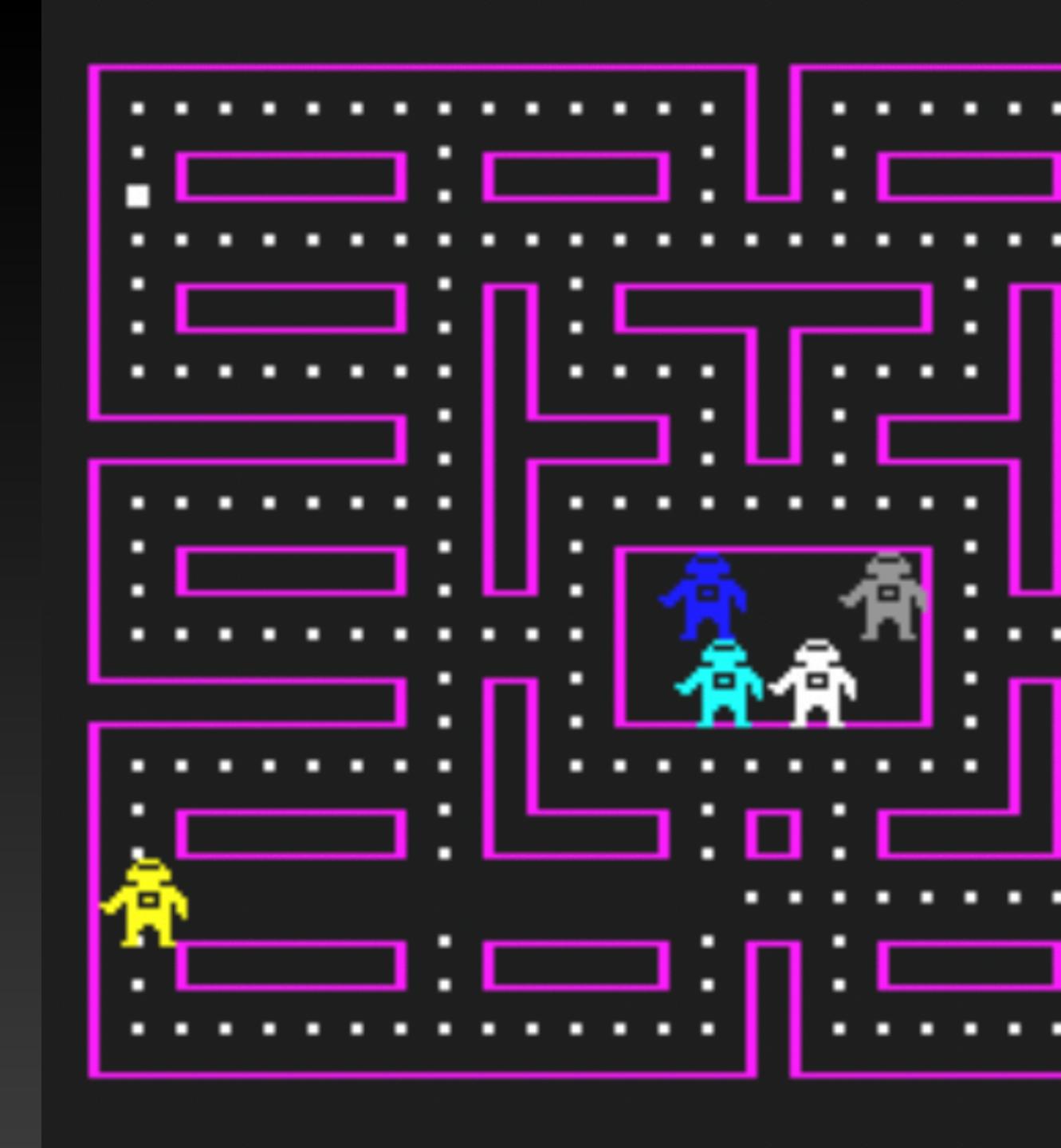

- 8bitworkshop is a web-based IDE for programming legacy 8bit platforms

- Primarily assembler and C targeting 6502 and Z80 CPUs

- Focused on video games

- Educational and fun

- It also supports Verilog!

# History of Arcade Games

- Arcade games in early 1970s

were discrete logic designs

- Used binary counters to generate sync signals

- Maybe a small ROM for sequencing and bitmaps, but no code

- It's educational and fun to reproduce them in Verilog

Verilog -

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

```

module hvsync_generator(clk, reset, hsync, vsync, display_on, hpos, vpos);

input clk;

input reset;

output reg hsync, vsync;

output display_on;

output reg [8:0] hpos;

output reg [8:0] vpos;

// declarations for TV-simulator sync parameters

// horizontal constants

parameter H_DISPLAY

= 256; // horizontal display width

= 23; // horizontal left border (back porch)

parameter H_BACK

= 7; // horizontal right border (front porch)

parameter H_FRONT

= 23; // horizontal sync width

parameter H_SYNC

// vertical constants

parameter V_DISPLAY

= 240; // vertical display height

= 5; // vertical top border

parameter V_TOP

parameter V_BOTTOM

= 14; // vertical bottom border

= 3; // vertical sync # lines

parameter V_SYNC

// derived constants

= H DISPLAY + H_FRONT;

parameter H_SYNC_START

= H_DISPLAY + H_FRONT + H_SYNC - 1;

parameter H_SYNC_END

parameter H_MAX

= H_DISPLAY + H_BACK + H_FRONT + H_SYNC - 1;

parameter V_SYNC_START

= V_DISPLAY + V_BOTTOM;

= V_DISPLAY + V_BOTTOM + V_SYNC - 1;

parameter V_SYNC_END

parameter V_MAX

= V_DISPLAY + V_TOP + V_BOTTOM + V_SYNC - 1;

wire hmaxxed = (hpos == H_MAX) || reset;

// set when hpos is maximum

wire vmaxxed = (vpos == V_MAX) || reset;

// set when vpos is maximum

// horizontal position counter

always @(posedge clk)

begin

hsync <= (hpos>=H_SYNC_START && hpos<=H_SYNC_END);

if(hmaxxed)

hpos <= 0;

else

hpos \leq hpos + 1;

end

```

#### **8bitworkshop Example Modules**

- Video sync generator

- Bitmap character display

- Switch and paddle input

- Sprites

- Sound

- ALU, CPU

- Multiple modules integrated into 16-bit computer design

# Assembly Support

- IDE can compile custom assembly languages defined by JSON

- Used for custom CPU designs

```

"name":"femto16",

"width":16,

"vars":{

"reg":{"bits":3, "toks":["ax", "bx", "cx"

"unop":{"bits":3, "toks":["zero","loada",

"binop":{"bits":3, "toks":["or","and","xo

"imm5":{"bits":5},

"imm8":{"bits":8},

"imm16":{"bits":16},

"rel8":{"bits":8, "iprel":true, "ipofs":1

"rules":[

"bits":["000

{"fmt":"~binop ~reg,~reg",

"bits":["000

{"fmt":"~unop ~reg",

{"fmt":"~binop ~reg,[~reg]", "bits":["000

"bits":["010

{"fmt":"mov [~reg],~reg",

"bits":["001

{"fmt":"mov ~reg,[~imm8]",

{"fmt":"mov [~imm8],~reg", "bits":["001

{"fmt":"~binop ~reg,#~imm8", "bits":["11"

{"fmt":"~binop ~reg,@~imm16","bits":["000

{"fmt":"~binop ~reg,[~imm16]", "bits":["0

```

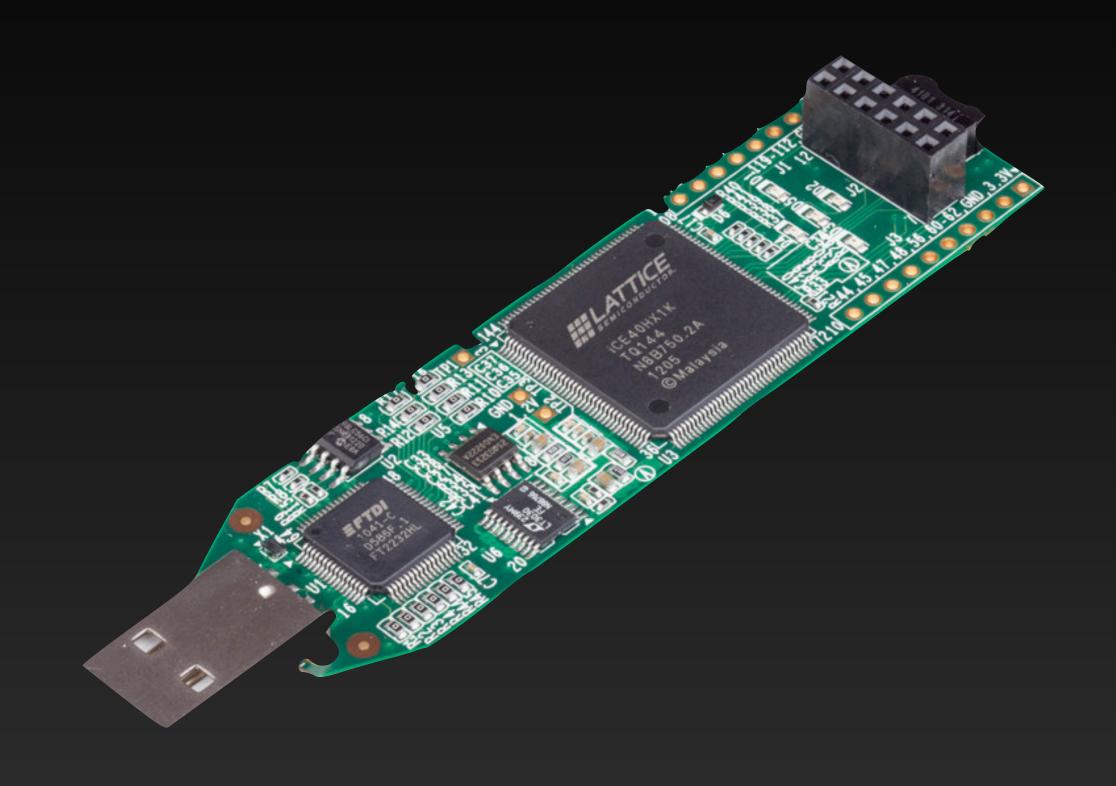

# FPGAs

- Example code modified to run on Lattice FPGAs

- Icestorm toolchain and Yosys

- Drives a composite CRT, need a few resistors to get the levels needed

## Links

- https://8bitworkshop.com/verilog

- https://github.com/sehugg/8bitworkshop

- https://github.com/sehugg/fpga-examples

- "Designing Video Game Hardware in Verilog"

### Thanks!

Steven Hugg

@sehugg

info@8bitworkshop.com