####

# **IRSIM: A Switch-Level Simulator** and Dynamic Power Analysis Tool

Jason Liang, Timothy Edwards

3 November 2022

# Introduction

- Originally developed for fast logic simulations before HDLs

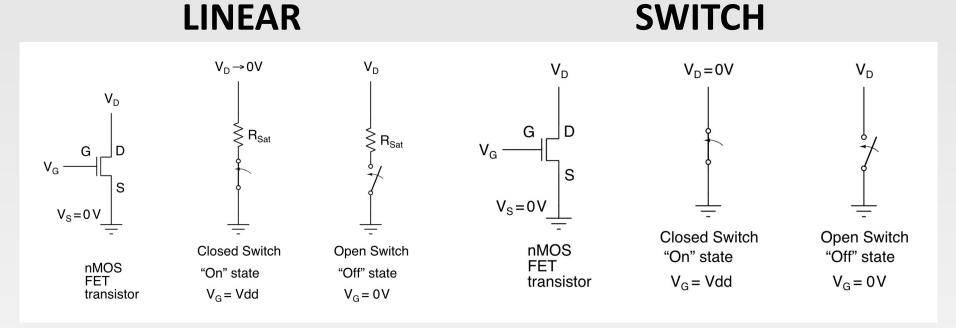

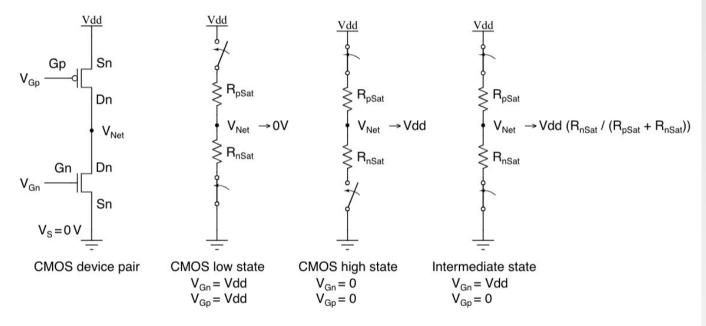

- Two types of transistor models for simulation: switch and linear

- Includes a less advertised dynamic power analysis tool

- One of few open source tools that can do dynamic power analysis

- OpenSTA (power analysis using .lib files)

## Simulation

- Supports Verilog-style testbench commands for verification and simulation of circuit (at and every)

- Simulation by scheduling events

- User feeds stimuli into interpreter

- Each stimulus provided is an event to be scheduled

- If a circuit is modified and resimulated, only the parts that have been changed are resimulated

- Events are timed approximately using an RC constant

## Simulation

| logic anal | /zer display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Zoom        | Base W        | Vindow | Print |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|--------|-------|

| 1059.12    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |               | 10     | 99.12 |

| OSC        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |               |        |       |

| div        | 01000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |               |        |       |

| clockp     | 11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01       11       10       00       01 <td< td=""><td>10 00 01 11</td><td>. 10 00 01 11</td><td>10 00</td><td></td></td<> | 10 00 01 11 | . 10 00 01 11 | 10 00  |       |

| resetb     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |               |        |       |

| enable     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |               | _      |       |

| clockp[0]  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |               |        |       |

| clockp[1]  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |               |        |       |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |               |        |       |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |               |        |       |

# Simulation

- Event constitutes switching of transistor state, similar to state changes in Verilog simulations

- Performs orders of magnitudes faster than SPICE simulations but still slower than Verilog

- SPICE provides power analysis information but Verilog does not, users simply stuck to the main purposes of other tools and ignored IRSIM

## **Dynamic Power Analysis**

- Functioned as originally intended but lacked useful features

- Dynamic power is normally calculated using the equation at right

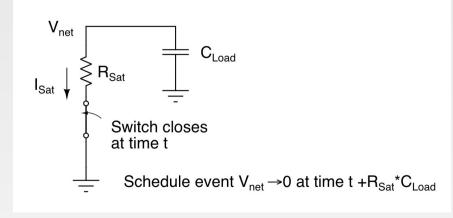

- IRSIM calculates switching energy of every transistor charging or discharging into capacitive load

## **IRSIM Before and After**

| BEFORE                                                  | AFTER                                                                      |

|---------------------------------------------------------|----------------------------------------------------------------------------|

| Supported only one nFET and one pFET device type        | Supports an arbitrary number<br>of FET device types                        |

| Supported simulation under a single power supply        | Supports simulation under multiple power supply                            |

| Needed to have commands<br>for verifying power behavior | Supports commands for power<br>visualization over given<br>simulation time |

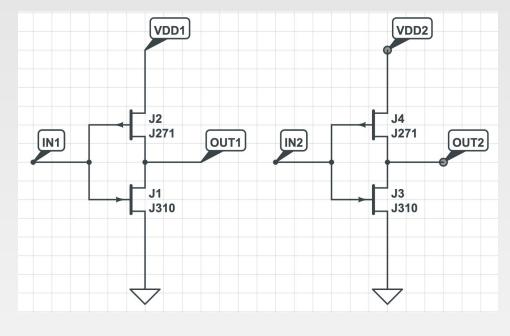

## **Multiple Device Support**

- ".sim" file is netlist of device characteristics in circuit, typically generated from layout tool

- Contains 'x' device type for subcircuit defining arbitrary circuit component beyond transistor/resistors/capacitors

- Updated to include device keyword for mapping foundry device models to IRSIM pFET and nFET devices:

- device nfet|pfet <device name>

- Specify custom resistance types

- resistance <device name>

static|dynamic-high|dynamic-low <width>

<length> <resistance>

- Device parameter files after this update: <u>https://github.com/RTimothyEdwards/open\_pdks/tree/mas</u> <u>ter/sky130/irsim</u>

## **Multiple Power Domain Support**

- Effective for dual-voltage domains with thick and thin oxide devices or standby power domains

- Specify a second power source using vsupply

- vsupply <power name> <power>

- After each step time, total energy is accumulated instead of total capacitance:  $\Sigma(CV^2)$ , saves computation time

School of Engineering

## **Multiple Power Domain Support**

• Example commands to support this:

```

# declare all of the power node names

power <net name>

...

```

```

# declare the ground node

ground <ground name>

```

```

# initialize logic high nodes and logic low nodes

h <node>

...

l <node>

...

# optionally, toggle signals

every <time> {toggle net}

```

```

# set voltage values

vsupply <power net> <voltage value>

```

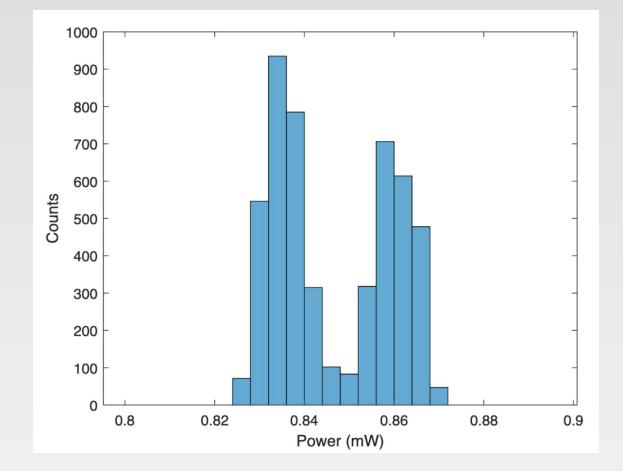

## Histogramming

Power visualization tool that allows user to visualize power behavior while simulating circuit

# set up circuit (voltage, power supply, etc...) powlogfile /dev/null powtrace \* powstep

# initialize the histogram with the minimum and maximum power range # and optionally the number of buckets, 20 default powhist init [min] [max] <buckets>

# if the histogram structure has been initialized, use the power # estimation formula to record the power and store it in the # histogram, otherwise, throw an error every <n> {powhist capture}

# simulate circuit indicated by time argument, capture power every n nanoseconds s <time>

# clear the histogram data and free the memory powhist reset

# print captured histogram data stored powhist print

#### Histogramming

```

File Console Edit Interp Prefs History Help

parallel txtors: n-channel=868 p-channel=920

time = 500.000ns

time = 1000.000ns

time = 1500.000ns; there are 4 pending events

Main console display active (Tcl8.6.12 / Tk8.6.12)

(irsim) 16 % source files/test.tcl

Supply Voltage = 1.80 Volts at VPWR

Power display enabled

time = 101500.000ns; there are 3 pending events

Histogram of power: 0.00 \rightarrow 101500.000 (bucket size = 0.01)

0.80 -

0.81

0

0.81 -

0.82

0

0.82 -

0.83 203

0.84 4457

0.83 -

0.84-0.859590.85-0.8621000.86-0.8722780.87-0.880

0.88 - 0.89

0

0.89 -

0.90

0

(irsim) 17 %

```

#### Histogramming

←UCSD School of Jacobs Engineering

## Conclusion

- Three major updates to IRSIM:

- multiple nFET/pFET device support

- multiple power voltage domain support

- power visualization command-line package

- Future work includes modifying delay and voltage compute model to accommodate parasitic interconnect delay (file format parsing)

- Repository link: <u>https://github.com/RTimothyEdwards/irsim</u>

- Acknowledgements: Dr. Tim Edwards and the Google Summer of Code program for facilitating and mentorship