### ACCESSIBILITY OF CHIP DESIGN TO THE NON-PROFESSIONAL

Alex Goldstein (<u>Alex\_Goldstein@outlook.com</u>), Tim Edwards, Ph.D. (<u>tim@opencircuitdesign.com</u>)

### Project Overview

# 01

Design a microchip that will fulfill a certain purpose and detail its functionality in Verilog Code

# 02

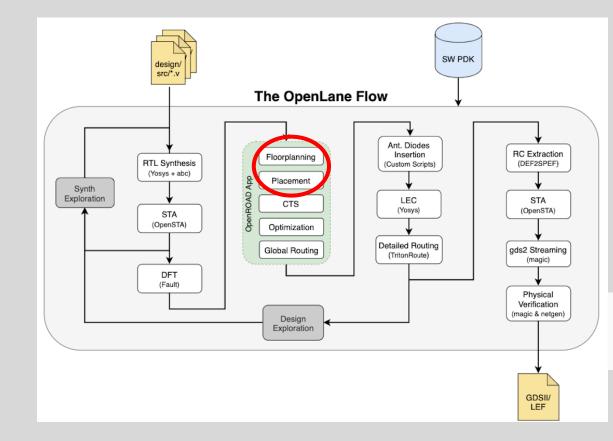

Create a potential chip layout to be fabricated using the OpenLANE software 03

Submit the chip layout to the Efabless Open MPW 7 Shuttle to be fabricated

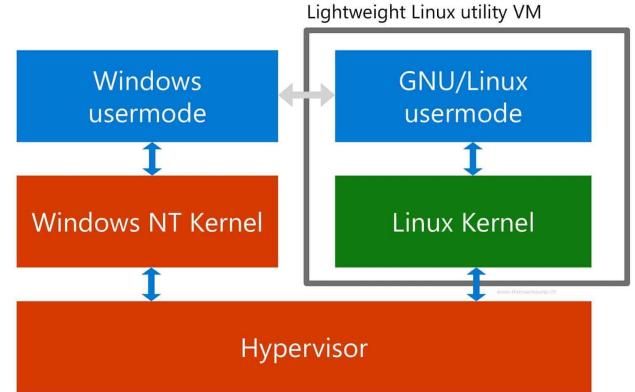

### WSL 2 architecture overview

Setting Up the Synthesis Environment

- OpenLANE only runs in a Unix-based environment

- About 80% of home computers run Windows

- We can get around this by utilizing the "Windows Subsystem for Linux (WSL)"

## What About Dependencies?

- Almost all of the Dependencies can be installed as normal through the terminal

- The Docker Daemon cannot be run in the terminal on its own

- The Docker Desktop Application allows us to still use the daemon through the engine's WSL 2 Integration

| Settings | 5                     |            |                                                               |                             |                   |         |

|----------|-----------------------|------------|---------------------------------------------------------------|-----------------------------|-------------------|---------|

|          | General               |            |                                                               | WSL Integration             |                   |         |

| 0        | Resources             | (          | Configure which WSL 2 distros you want to access Docker from. |                             |                   |         |

|          | Advanced              |            | Z Enable interpretenting                                      | egration with my default V  | VSL distro        |         |

|          | Proxies               | E          | Enable integra                                                | tion with additional distro | s:                |         |

|          | Network               |            | Ubuntu                                                        | -20.04                      |                   |         |

|          | WSL Integration       | ſ          |                                                               |                             |                   |         |

| -        | Docker Engine         | l          | Refresh                                                       |                             |                   |         |

| È.       | Experimental features |            |                                                               |                             |                   |         |

| ۲        | Kubernetes            |            |                                                               |                             |                   |         |

| Ð        | Software updates      |            |                                                               |                             |                   |         |

| *        | Extensions            |            |                                                               |                             |                   |         |

|          |                       |            |                                                               |                             |                   |         |

|          |                       |            |                                                               |                             |                   |         |

|          |                       |            |                                                               |                             |                   |         |

|          |                       |            |                                                               | Canc                        | el Apply & Restar | t       |

|          |                       | RAM 3.17GB | CPU 0.07%                                                     | 🖹 Not connected to Hub      |                   | v4.12.0 |

\$ gh repo clone

AlexanderJGoldstein/chaos\_automaton\_Summer\_2022 -- -depth=1

- \$ cd chaos\_automaton\_Summer\_2022

- \$ mkdir dependencies

- \$ export OPENLANE\_ROOT=\$PWD/dependencies/openlane\_src

- \$ export PDK\_ROOT=\$PWD/dependencies/pdks

- \$ export PDK=sky130B

- \$ make setup

- \$ make chaos\_subarray

- \$ make user\_project\_wrapper

- \$ make ship

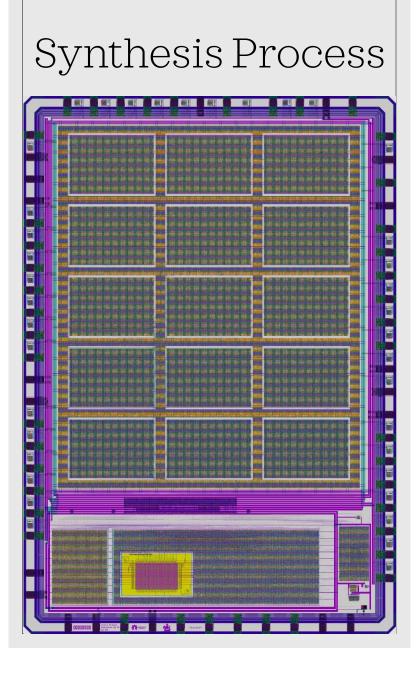

## The Final Design

• 3 by 5 array of subarrays (15 total)

- Each subarray is a 10 x 6 array of chaos cells (60 per subarray)

- $\circ~$  There are 900 chaos cells in total!

- 63.68% Utilization

The final layout for a single completed subarray

A close-up of 0.4% of the subarray (25,000% magnification)

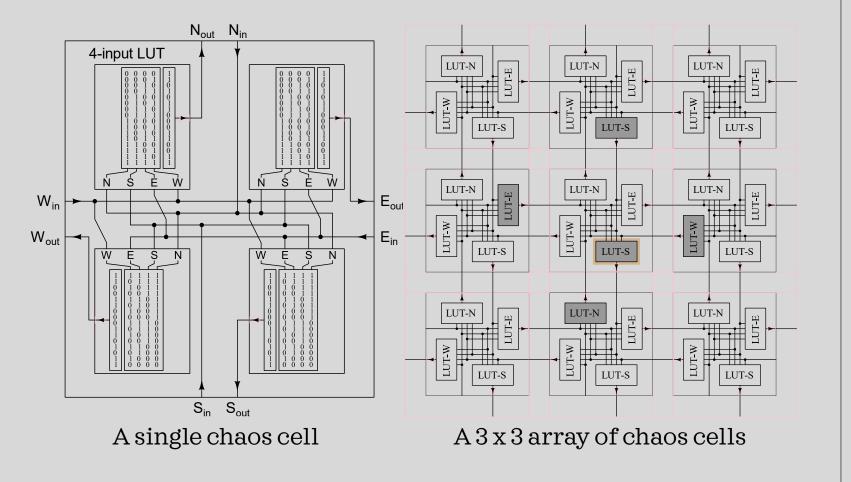

### What is this "Chaos Automaton?"

- A large array of interconnected LUT chips

- The array (apart from programming) is completely asynchronous

### What is this "Chaos Automaton?"

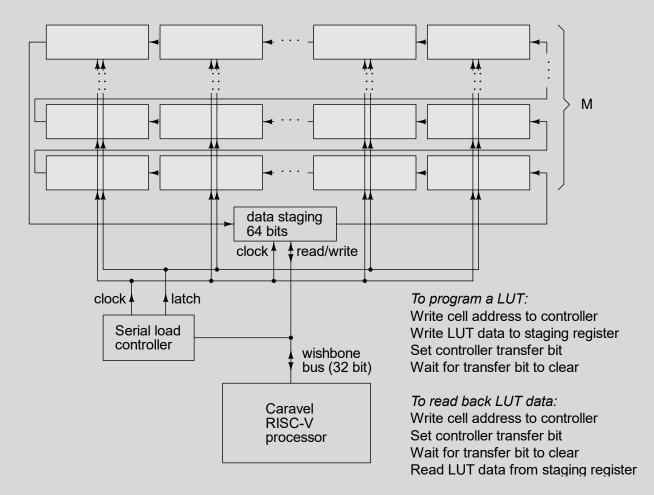

These LUTs are programmed individually by the Caravel Wrapper's RISC V CPU

WHYTHIS DESIGNFORA CELLULAR AUTOMATON?

The Chaos Automaton is an array-based (cellular) design. One separate goal was to see just how large of an array could fit within the user project area.

### Custom Settings

• set ::env(ROUTING\_CORES) 16

• set ::env(MACRO\_PLACEMENT\_CFG) \$script\_dir/macro\_placement.cfg

Subarray:

- set ::env(DIE\_AREA) "0 0 825 585"

- set ::env(PL\_TARGET\_DENSITY) 0.45

### What Were the Obstacles?

# 01

#### Memory Consumption

02

#### Documentation

03

Execution Time

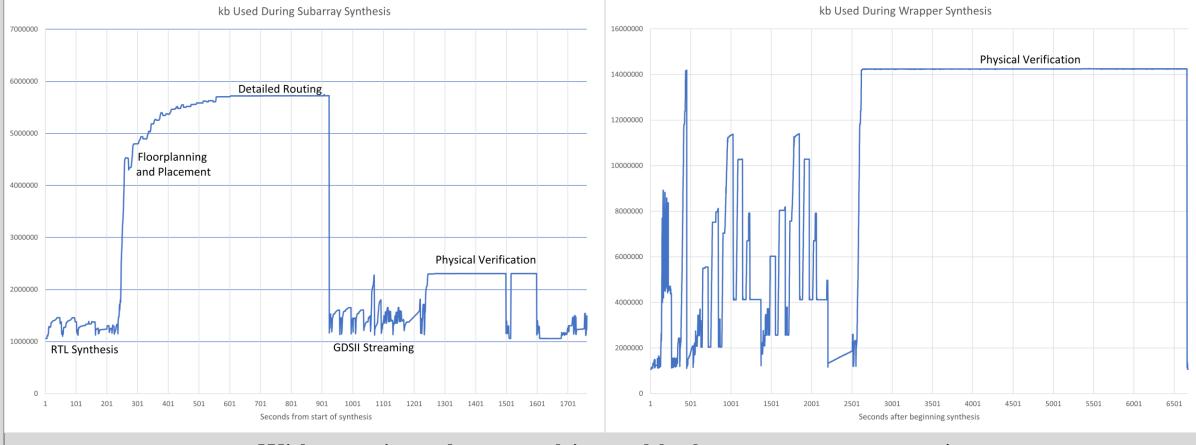

### Obstacle 1: Memory Consumption

Without using subarrays, this would take even more memory!

### Obstacle 2: Documentation

| FP_PDN_VOFFSET     | The offset of the vertical power stripes on the metal<br>layer 4 in the power distribution network<br>(Default: 16.32)                                                                          |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FP_PDN_VPITCH      | The pitch of the vertical power stripes on the metal<br>layer 4 in the power distribution network<br>(Default: 153.6)                                                                           |  |

| FP_PDN_HOFFSET     | The offset of the horizontal power stripes on the metal layer 5 in the power distribution network (Default: 16.65 )                                                                             |  |

| FP_PDN_HPITCH      | The pitch of the horizontal power stripes on the metal<br>layer 5 in the power distribution network<br>(Default: 153.18)                                                                        |  |

| FP_PDN_AUTO_ADJUST | Decides whether or not the flow should attempt to re-<br>adjust the power grid, in order for it to fit inside the<br>core area of the design, if needed.<br>1=enabled, 0 =disabled (Default: 1) |  |

|                    | <pre>list {vccd1} {vccd2} {vdda1} {vc }</pre>                                                                                                                                                   |  |

|                    | list {vssd1} {vssd2} {vssa1} {vs<br>G PINS_DEFINES) "USE_POWER_PINS"                                                                                                                            |  |

|                    | RO_HOOKS).* vccd1 vssd1 vccd1 v                                                                                                                                                                 |  |

|                    |                                                                                                                                                                                                 |  |

### Obstacle 3: Execution Time

| gh repo clone | make setup                 | make chaos_subarray | <pre>make user_project_wrapper</pre> |

|---------------|----------------------------|---------------------|--------------------------------------|

| 45 Seconds    | 1 Minute and<br>21 Seconds | 30 Minutes          | 1 Hour and 45 Minutes                |

### 2 Hours and 15 Minutes per Synthesis

### Conclusion

Overall, this research has proved that it is possible for a high school student to effectively use current EDA technologies, which acts as proof that more people are able to enter the Electronic Design space.

#### Key Links:

- Chaos Automaton Repository: <u>https://github.com/AlexanderJGoldstein/chaos\_automaton\_Summer\_2022</u>

- Caravel Harness Repository: <u>https://github.com/efabless/caravel</u>

- Caravel User Project Repository: <u>https://github.com/efabless/caravel\_user\_project</u>

- OpenLANE Documentation: <u>https://OpenLANE-</u> <u>docs.readthedocs.io/en/rtd-develop/</u>

- WSL Documentation: <u>https://learn.microsoft.com/en-us/windows/wsl/</u>

#### Acknowledgements

Poolesville High School Science, Math, and Computer Science Program